Prototype

transistors promise speedy chips

By

Kimberly Patch,

Technology Research NewsComputer chips run faster as the transistors that make up their logic gates get smaller or in some other way more efficient. Most chip speed improvements in the last 20 years have been made simply by shrinking the transistor in order to shorten the path an electrical signal must travel to turn on a logic gate.

For the past decade or so, however, researchers have been wondering aloud whether this type of improvement can continue. The two main challenges are finding ways to etch smaller paths for electrons into the silicon chips, and keeping electrons contained within the paths to prevent the volt leakage that makes chips inefficient.

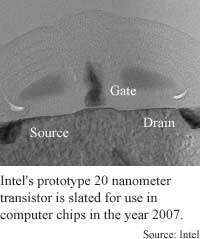

Researchers at Intel Corp. have gone a long way toward continuing the improvement until at least the year 2007 with two generations of prototype transistors that use the common single gate technology found in existing computers. The prototypes are 30 and 20 nanometers long, and the smaller one is less than a third the size and more than 10 times faster than those found on today's chips, according to Gerald Marcyk, director of Intel's Components Research Lab.

To make the 20-nanometer transistor, the Intel researchers "played some processing tricks in order to make the lines that small," Marcyk said. Intel will detail those tricks next year, probably at the Device Research Conference in Seattle in February, said Marcyk.

Although researchers from the University of California at Berkeley late last year made a smaller, 15-nanometer prototype that in theory could be made as small as eight nanometers, it used a more complicated double gate design.

Conventional transistors have three electrodes. Electrical current enters through a source electrode on one end of the transistor, exits through a drain electrode on the other end, and the rate of flow is controlled by a single gate electrode on top of the device. The double gate design, with electrodes both on the top and bottom of a transistor, potentially controls volt leakage better, but makes the devices more difficult to manufacture.

To keep volt leakage down using the single gate design, the Intel researchers used less voltage and shrank the layer of silicon oxide used by the control gate from today's 4-nanometer thickness to 0.8 nanometers. The result is a three-atom-thick layer of two oxygen and one silicon atom.

The 30 nanometer prototype uses 0.85 volts and will eventually be used to build 500-million-transistor computer chips that run as fast as 20 gigahertz, or billion cycles per second; the 20 nanometer prototype uses 0.75 volts and will allow for chips that contain up to one billion transistors and run as fast as 25 gigahertz, Marcyk said.

For comparison, today's Pentium 4 processors use about 42 million 70-nanometer transistors, 1.3 volts of power to push the electrons through those transistors, and run as fast as 1.7 gigahertz. The Pentium processors released in 1995 used 5.5 million 2.5 volt, 350-nanometer transistors and had a top speed of 133 megahertz, or million cycles per second; the 386 processor, first released in 1985, used 275,000 5-volt, 1,500- and 1,000-nanometer transistors and had a top speed of 33 megahertz.

Intel's 30- and 20-nanometer transistors are successive generations slated for use in products in 2005 and 2007, according to Marcyk. Intel's next generation chip, slated for release in 2003, will use 50-nanometer transistors, according to Intel.

The researchers are currently working on making these newest generations of prototypes manufacturable, said Marcyk. "The challenge, of course, is how you take something from a research project into high-volume manufacturing," he said. To make the prototypes, the researchers tweaked the current deep ultraviolet photolithography process, which uses 248-nanometer lightwaves. "That's good for making a handful of transistors to demonstrate a research concept. This is not a manufacturing process that you take into high-volume and make 100 million microprocessors," Marcyk said.

To manufacture the 20-nanometer transistors in bulk, the researchers are looking to another research project, a photolithography process that uses 13-nanometer extreme ultraviolet light that is scheduled to be ready for practical use in 2006 or 2007, said Marcyk.

In the photolithography process, lightwaves are used to pattern the lines of a transistor, and the resolution of a line is proportional to the wavelength of light and the aperture of the lens the light shines through. Current manufacturing processes use 248-nanometer light. Lab projects have shown it may be possible to use 157-nanometer light in similar processes, but that's still not small enough to manufacture 20-nanometer transistors in bulk, Marcyk said.

One difficulty in using 13-nanometer extreme ultraviolet light is the light will not go through a lens, and so must be guided using mirrors instead. Materials like aluminum, however, cannot be part of reflective surface because they absorb that wavelength of light. "You end up with a complex multilayer mirror on the surface of the lenses, so there are some enormous challenges there," said Marcyk.

The first demonstration of a working, 20-nanometer silicon transistor is an impressive accomplishment that gives the semiconductor industry a glimmer of hope that alternative transistor structures may not be needed for several more technology generations, said Tsu-Jae King, an associate professor of engineering and computer sciences at the University of California at Berkeley, and director of its microfabrication laboratory. In addition, extreme ultraviolet lithography shows promise for manufacturing integrated circuits with 20-nanometer feature sizes, she said. "Cost is the only real issue."

However, more data, including an assessment of leakage current and information about how the researchers were able to fashion ultra-shallow source and drain junctions is needed before a fair assessment can be made about the transistor's practicality, King said. "The primary challenge in scaling bulk silicon transistor technology to sub 30-nanometer gate length is suppression of leakage current," she said.

One solution many in the industry are working on is replacing the silicon oxide with a thicker layer of a high-K material, which allows electricity to pass through it more quickly, she said. These materials come with a challenge, however. "Degradation of [electron] mobility, which results in degraded drive current, is an issue for many of the high-K dielectrics being investigated today, she said.

The Intel researchers are working to find high-K materials in order to push the size limit further, Marcyk said. "The purpose here is... to extend the single gate concept as far as possible until it breaks, and then we'll start using more complex alternatives," said Marcyk. "We have the data that shows that we can get to 2007 with existing material. And when we look at the materials and the structures we can clearly go beyond the end of the decade," he said.

The 20-nanometer prototype is impressive, said Phillip First, an associate professor of physics at Georgia Tech. One potentially tricky part of making such small transistors in bulk, however, is keeping down the defect rate, he said. "When you get down to things that size -- three atoms thick and 20 nanometers -- one of the critical things [is] the success rate because... a single defect could kill the device, whereas at the larger size scale you may be able to tolerate a defect within the device and still have it operate."

At some point there is a limit to how small electron paths can be, First added. This is because of the split nature of electrons, which act more like waves than particles as the spaces they're confined to get smaller. "Ultimately things will have to be designed differently in order to account for quantum effects -- the wave nature of the electron," he said.

The Intel researchers were Robert Chau, Mark Doczy, Brian Doyle, Pat Stokely, Dan Lionberger, and Nancy Paulson. Chau presented the research at the Silicon Nanoelectronics Workshop in Kyoto on June 12, 2001. The research was funded by Intel.

Timeline: 4-6 years

Funding: Corporate

TRN Categories: Integrated Circuits; Semiconductors

Story Type: News

Related Elements: Technical paper, "30 nm and 20 nm Physical Gate Length CMOS Transistors," Presented at the Silicon Nano Electronics Workshop in Kyoto, June 12, 2001.

Advertisements:

June 27, 2001

Page One

Chemists concoct tiny lasers

Slimmer chips handle fast nets

Prototype transistors promise speedy chips

Molecules make short-term memory

Micromachine parts relax into place

News:

Research News Roundup

Research Watch blog

Features:

View from the High Ground Q&A

How It Works

RSS Feeds:

News

Ad links:

Buy an ad link

| Advertisements:

|

|

Ad links: Clear History

Buy an ad link

|

TRN

Newswire and Headline Feeds for Web sites

|

© Copyright Technology Research News, LLC 2000-2006. All rights reserved.